09.01.2026 TF-20

Mir ist neulich eine TF-20 zugeflogen, natürlich defekt. Fritz hat mir dafür schon die Bootdiskette zugesand, funktioniert natürlich nicht. Nach bisherigen Ermittlungen will das A-Laufwerk nicht, wird angesprochen kommt aber nicht zum Ende.

Hierzu muss man natürlich wissen, die TF-20 ist ein vollständiger CP/M-Rechner mit Z80 CPU und 64kByte RAM, nur leider ohne Konsolenschnittstelle. Beim Einschalten erwartet er im Laufwerk A eine Boot-Diskette, entweder wie ursprünlich vorgesehen für den HX-20 und säpter für den PX-8/4.

Erstmal die Diskettenlaufwerke ausgebaut (Epson TD-F200A DS, DD, 2x40Tr.) und an den Prof angeschlossen, haben glücklicherweise den Standard Shugart 34pol BUS. Köpfe werden nur unter lautem Protest bewegt, die Linearmotoren kleben an der Führungsstange. Im 1.Laufwerk wird der Kopf nicht bewegt,Ansteuerung defekt. Das zweite konnte zur Mitarbeit überzeugt werden und erstmal eine Diskette formartiert, mangels geeignetem Epson Format auf IBM-PC DS,DD, 40Track ausgewichen, einige Dateien kopiert/gelesen – es gibt aber einige BDOS-Fehler „Diskette nicht bereit“. Für die weitere Untersuchung benötige ich erst einmal ein zuverlässiges 40Track Laufwerk – Fritz hat da was als Leihgabe liegen.

12.01.2026 Fehleranalyse die 2.

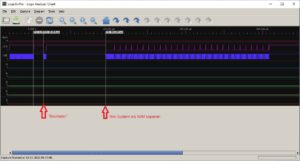

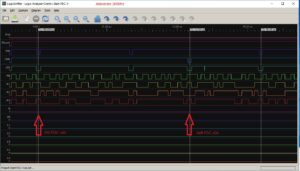

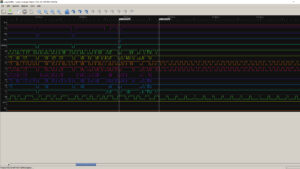

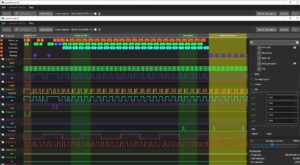

Zur weiteren Fehlereingrenzung habe ich mir das TF-20 Board näher angesehen. Mit dem Oszi zeigen die /CS Signale vom EPROM/FDC eine Aktivität – schon schlimmes befürchtet. Der Logic Analyzer brachte glücklicherweise etwas mehr Details ans Licht.

Am /CS-ROM sieht man den Zugriff sehr deutlich, zunächst wird das Ladeprogramm angesprochen welches dann das Minisystem ins RAM ab [0F800h] kopiert und dann gestartet. Im 3.Bild wird er FDC auf seinen beiden Adressen angesprochen [xAh und xBh].

Am /CS-ROM sieht man den Zugriff sehr deutlich, zunächst wird das Ladeprogramm angesprochen welches dann das Minisystem ins RAM ab [0F800h] kopiert und dann gestartet. Im 3.Bild wird er FDC auf seinen beiden Adressen angesprochen [xAh und xBh].

Also erstmal alles im grünen Bereich – EPROM und FDC scheinen zu laufen.

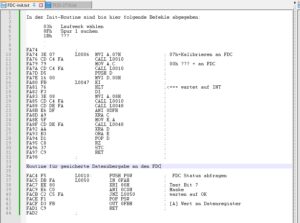

Bei der Gelegenheit das EPROM kopiert und Disassembliert, hier sieht man den „Bootloader“ und die rund 800Byte vom Minisystem.

16.01.2026 Analyse die 3.

Bei Fritz haben wir das EPSON Laufwerk getestet – keine zuverlässige Funktion, bei der Gelegenheit noch zwei neue Bootdisketten erzeugt und ein 40Tr TEAK für weitere Analysen als Leihgabe mitgenommen…

Auch damit ist kein BOOT möglich, Laufwerk wird angesprochen und nudelt bis zum „Sankt Nimmerlein“. Leider gibt es kein Monitorprogramm um die Fehlersuche zu unterstützen, hilfreich wäre ja schon zu wissen in welcher Endlosschleife er seine Zeit vertrödelt – da werden wohl noch viele Stunden für die Analyse nötig sein…

18.01.2026 Analyse die 4.

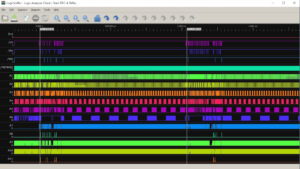

Der Logic Analyzer zeigt im 5Mhz-Modus zwei Sequenzen mit reger Tätigkeit mit dem FDC, danach tut sich nichts mehr. Zur besseren Analyse die Abtastrate auf 50Mhz erhöht, so kann man die Adresslage im Rahmen der Möglichkeiten eingrenzen. Die oberen vier Adressen sind immer High [Fxxxh], A0 ist mangels ausreichender Kanäle auch nicht berücksichtigt.

Der Logic Analyzer zeigt im 5Mhz-Modus zwei Sequenzen mit reger Tätigkeit mit dem FDC, danach tut sich nichts mehr. Zur besseren Analyse die Abtastrate auf 50Mhz erhöht, so kann man die Adresslage im Rahmen der Möglichkeiten eingrenzen. Die oberen vier Adressen sind immer High [Fxxxh], A0 ist mangels ausreichender Kanäle auch nicht berücksichtigt.

Nach diesem Bild werkelt er im Adressbereich F63xh und FCCxh. Laut dem Assemblerlisting ist das Minisystem zwischen F8xxh und FB20h angesiedelt.

Da stehen mir erstmal ganz viele Fragezeichen über meinem Kopf????????????…

20.01.2026 Analyse die 5.

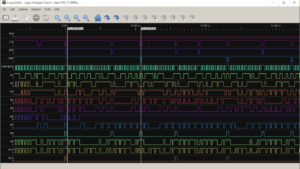

Neuer Ansatz, wie sehen die Daten zum/vom FDC aus, dazu noch das RDY Signal und ob ein INT erzeugt wird:

Im ersten Bild sieht man die Aktivitäten der Init-Routine und etwas gezoomt das jähe Ende. Ab da wartet die CPU auf einen INT vom FDC und wartet und wartet…

Im ersten Bild sieht man die Aktivitäten der Init-Routine und etwas gezoomt das jähe Ende. Ab da wartet die CPU auf einen INT vom FDC und wartet und wartet…

Anmerkung: Das RDY-Signal vom Laufwerk wird nicht ausgewertet, der Jumper ist auf High gesetzt.

Das deckt sich auch mit dem Assemblerlisting, hier werden nacheinander die Werte übergeben und schließlich mit dem INT auf Ausführung gewartet…

Das Diskettenlaufwerk funktioniert ohne Zweifel, die Bootdiskette hat auch im Track 0 Sektor 1 einen Bootloader, so liegt der Verdacht auf dem Datenseparator obwohl hier alle Signale an den Testpunkten wie im Handbuch aussehen.

Hier währe ein TIP aus euren Reihen sehr hilfreich…

21.01.2026 Analyse die 6.

Die bisherigen Analysen waren ja ganz lehrreich nur ohne konkrete Ergebnise bis auf die Tatsache das er bei der Initialisierung des FDC hängen bleibt. Nächster Ansatz die Schnittstelle vom/zum Diskettenlaufwerk „durchklingeln“. Siehe da ein TTL 7438 [Position 10E]der seine Ausgänge beharrlich auf LOW hält, zuständig für die Signale [In Use/HeadLoad, Motor ON, Direction Select und Step] wobei Motor ON nicht gesteuert wird, immer auf LOW.

Die bisherigen Analysen waren ja ganz lehrreich nur ohne konkrete Ergebnise bis auf die Tatsache das er bei der Initialisierung des FDC hängen bleibt. Nächster Ansatz die Schnittstelle vom/zum Diskettenlaufwerk „durchklingeln“. Siehe da ein TTL 7438 [Position 10E]der seine Ausgänge beharrlich auf LOW hält, zuständig für die Signale [In Use/HeadLoad, Motor ON, Direction Select und Step] wobei Motor ON nicht gesteuert wird, immer auf LOW.

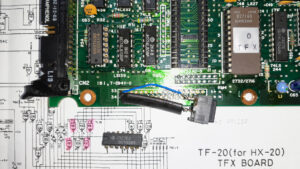

IC getauscht, um die Platine zu schonen einfach die Pinne abgeknipst und die Reste einzeln ausgelötet. In der Bastelkiste gab es nur ein 74LS38, sollte kein Problem sein und zur Not auswechselbar. Nochmals auf Funktion getestet, die Funktionen STEP, DIR, LOAD und Motor ON sind damit wieder OK.

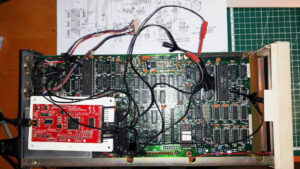

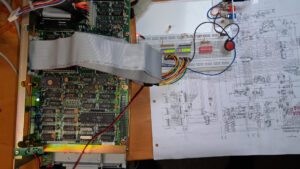

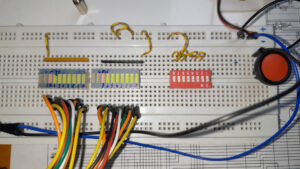

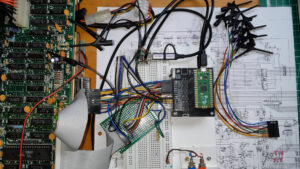

bisher bin ich davon ausgegangen das der EPROM Inhalt richtig im Speicher bei F800h landet, mangels Monitor ist das erstmal schlecht überprüfbar. Ein Testprogramm ist schnell geschrieben nur wie sehe ich das Ergebnis. Die V24 würde sich dazu anbieten, nur der verwendete SIO Baustein ist noch nicht in meinen Softwaretools aus dem Moppel „vorhanden“. Optional kann die Diskettenstation mit einer PIO 8255 ausgerüstet werden – gesagt getan, PullUps und eine entsprechende Fassung eingelötet. So stehen 3×8 Ports zur Verfügung.

Das mini Testprogramm schreibt wie üblich eine Wert ins RAM und liest es wieder aus, das gleiche nochmals mit dem negiertem Wert, wenn alles OK ist gehts zum nächsten Speicherplatz. Für die Anzeige schaufelt er die Start-, Endadresse und falls ein Fehler auftaucht auch diese über die PIO zu den LEDs. Hier hätte ich noch eine Verzögerung einbauen sollen, denn vom Reset bis zum Testende war es mir nicht möglich ein Foto zu machen 😉

Das ganze hat keinen Fehler entdeckt – gut eine Baustelle weniger.

Für das bessere Verständnis der TF-20 habe ich die Software mal näher betrachtet. Wenn das Mini-System aus dem EPROM nach F800h geladen wurde, Initialisiert es erstmal die SIO und den FDC, damit wird dann der eigentliche BOOTLoader von Diskette Tr.0/Sekt 1 geladen der anschließend das BDOS auf Adresse DB00h und das BIOS ab F200h lädt. Also alles wie bei einem normalen CP/M 2.0 System, es gibt nur kein CCP. Dies übernimmt dann der PX-8/HX-20…

Für die weiteren Analysen muss ich erstmal auf den neuen LogicAnalyzer mit 24Kanlen warten der mir das Geschen rund um den INT besser beleuchten kann.

Der neue LogicAnalyzer ist eingetroffen und nach den ersten Spielereihen die Erweiterung auf 48Kanäle nachbestellt, nun kann es mit der Fehleranalyse weitergehen.

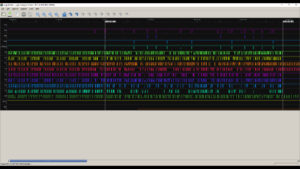

Alle Z80 Adr/Daten Leitungen sind an den Kanälen 25-48 angeschlossen die restlichen Z80 relevanten Signale an Kanal 1-9 und die TP3 „RD Daten“, TP6 „Fenster“ und TP5 „Daten CLK“ des FDC an Kanal 10-12 angeschlossen.

In der Analyse ist ab dem letzten Zugriff auf dem FDC „WR 0 an Port FBh“ dargestellt, danach folgt die INT Freigabe und der Haltepunkt bis /INT vom FDC ausgegeben werden soll…

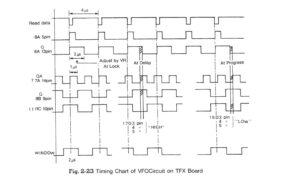

Die Datenbits sollen innerhalb des vorgegebenen Fensters eingelesen werden, beim ersten Bit scheint das zu stimmen, die restlichen liegen ausserhalb und werden nicht erkannt. So wartet der FDC bis zum Nimmerleinstag. Das war auch schon weiter oben meine Vermutung nur jetzt habe ich das komplette Umfeld im Blick.

So scheint es sich doch um ein Fehler im Datenseparator zu handeln, meine früheren Messungen mit dem Oszi waren nach Datenblatt eigendlich OK.

Diesen Bereich werde ich nochmals genauer untersuchen…

Hier das EPROM und BIOS als ZIP-Datei: (Stand 11.02.2026)